25 ++ Verilog シフトレジスタ 155911-Verilog 多ビット シフトレジスタ

Learn verilog Shift register

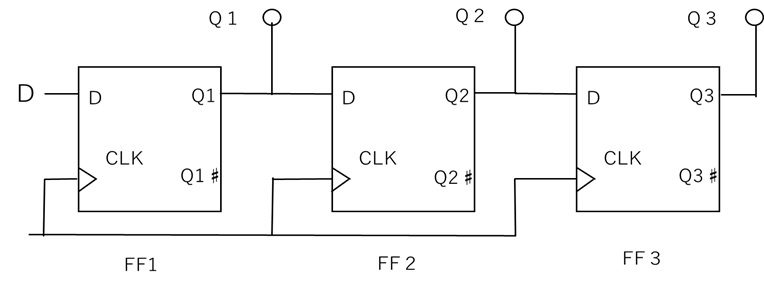

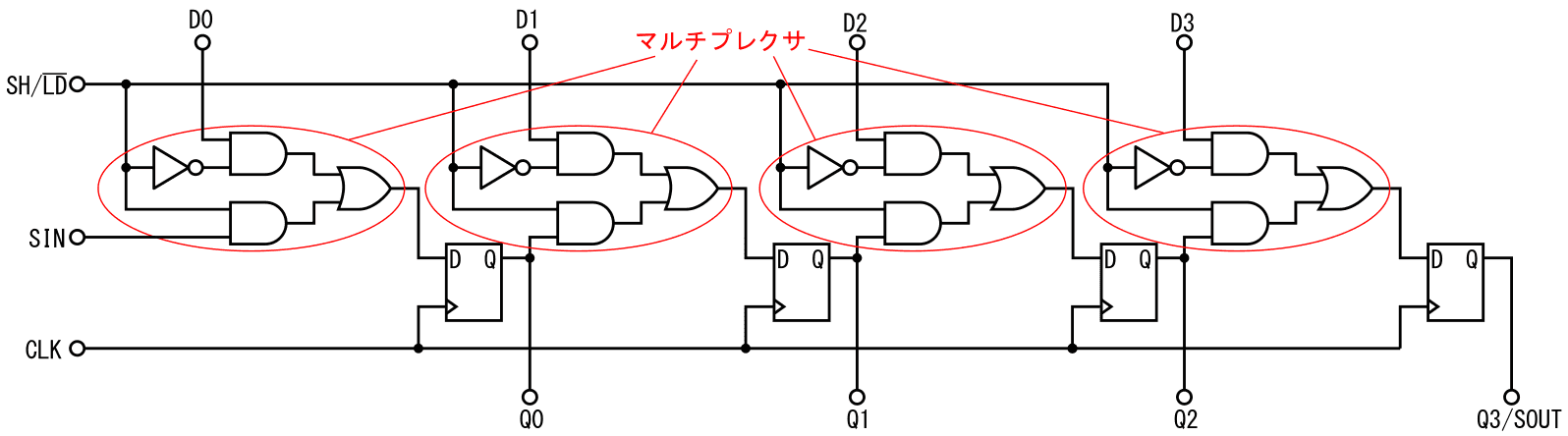

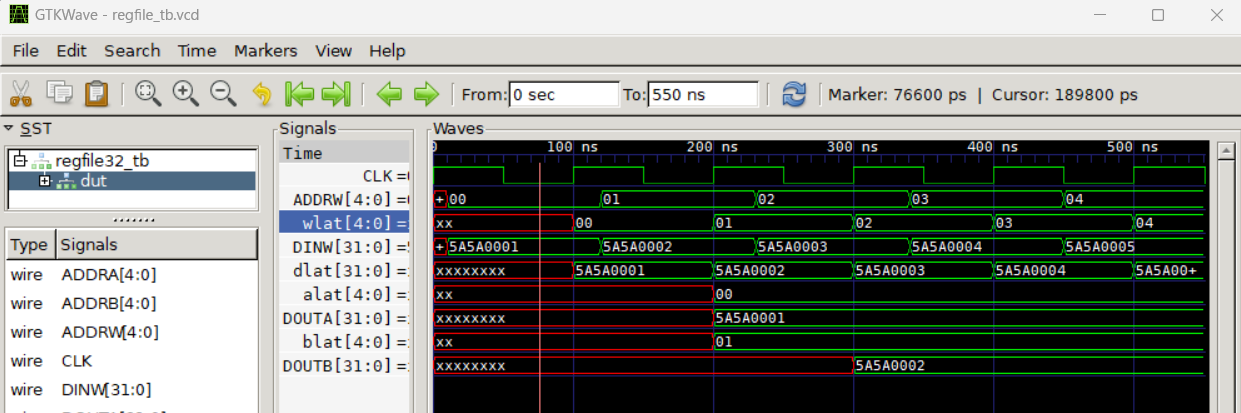

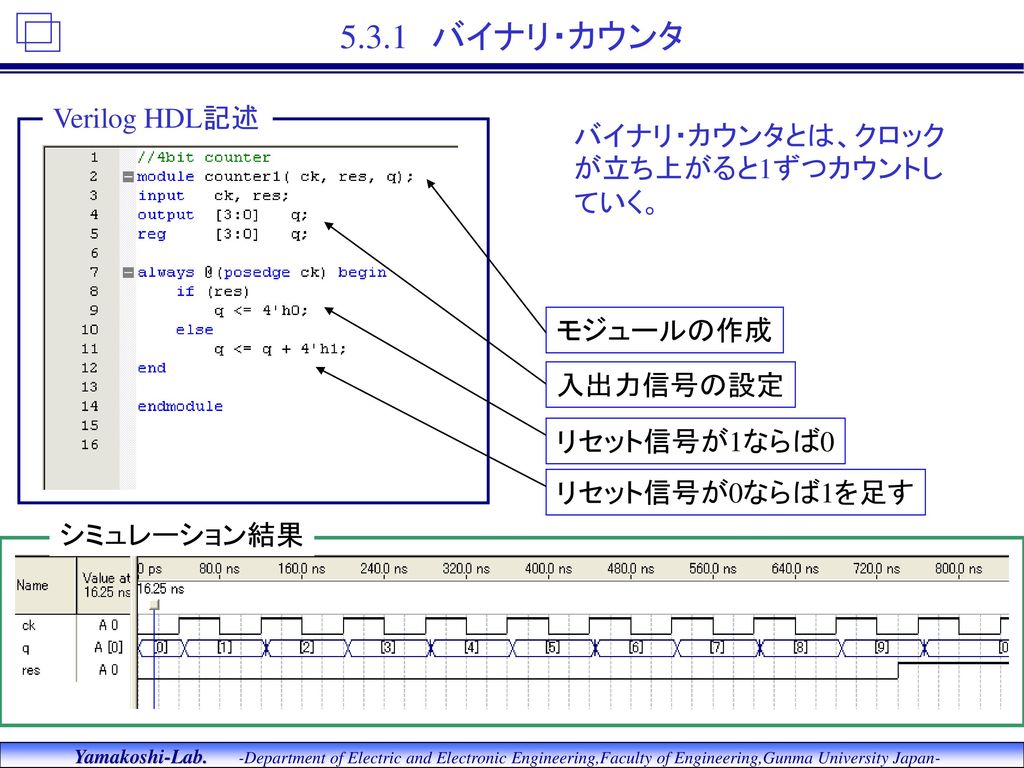

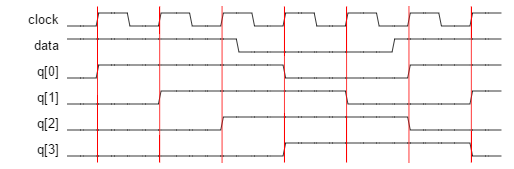

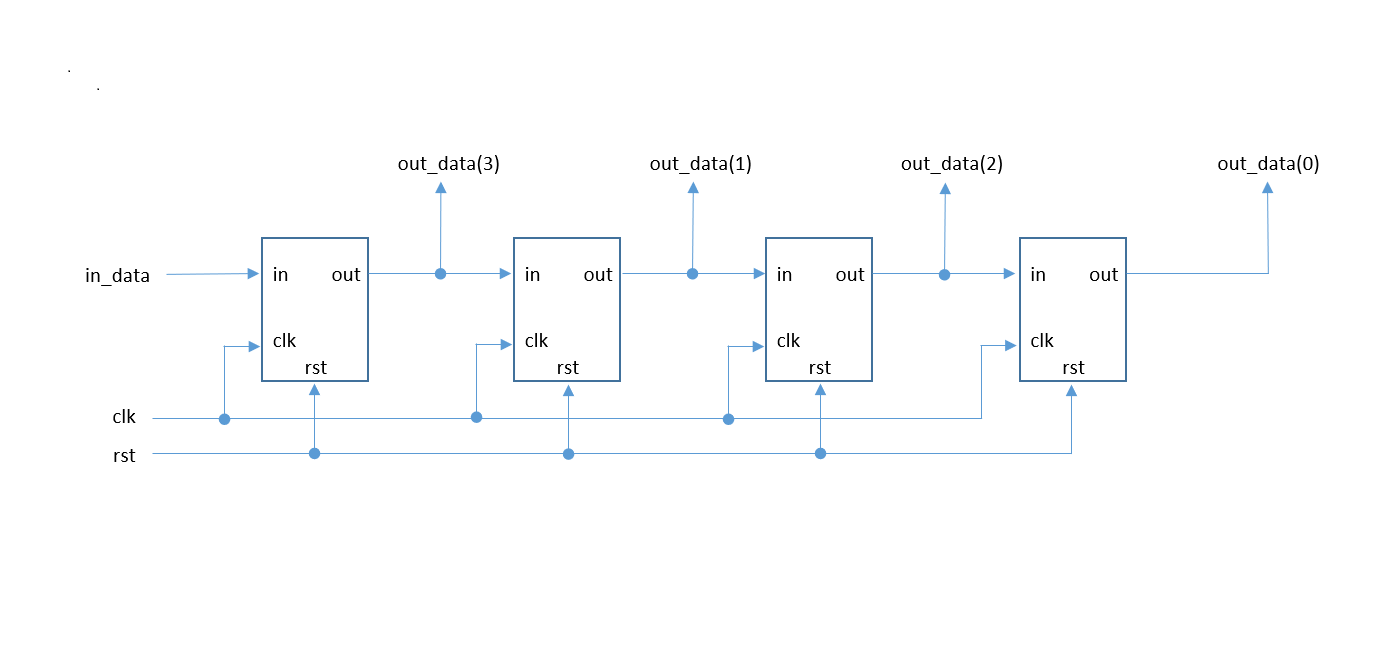

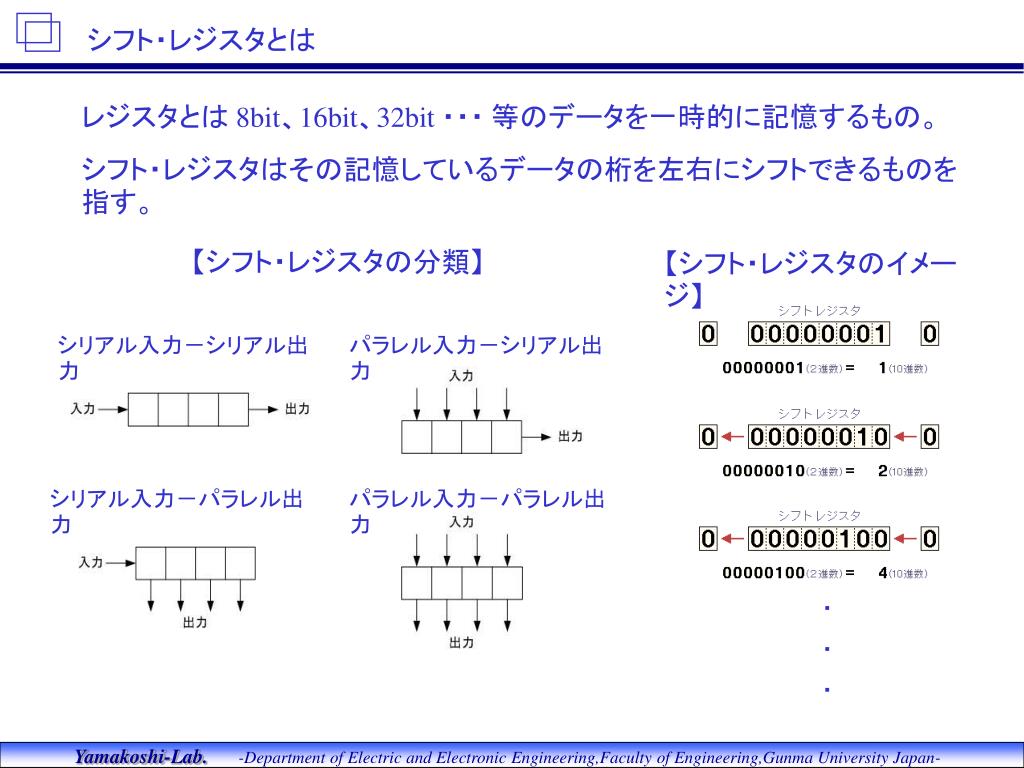

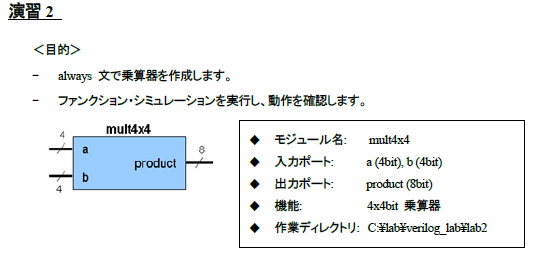

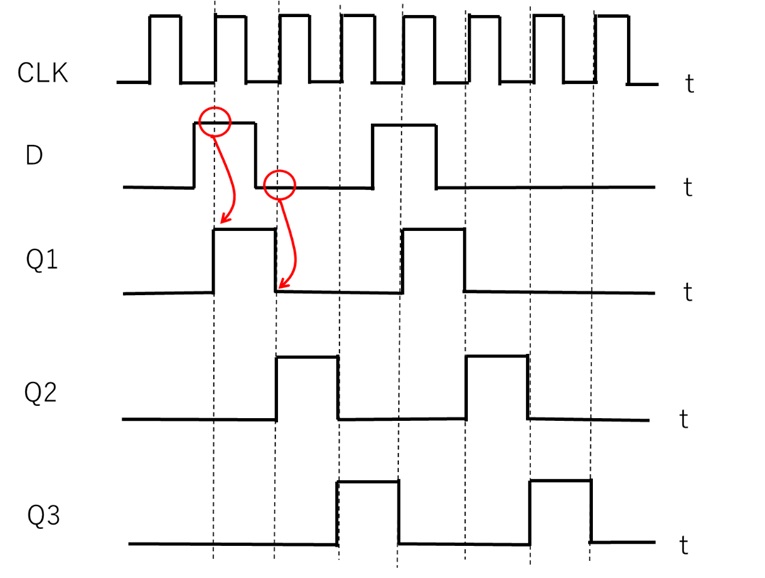

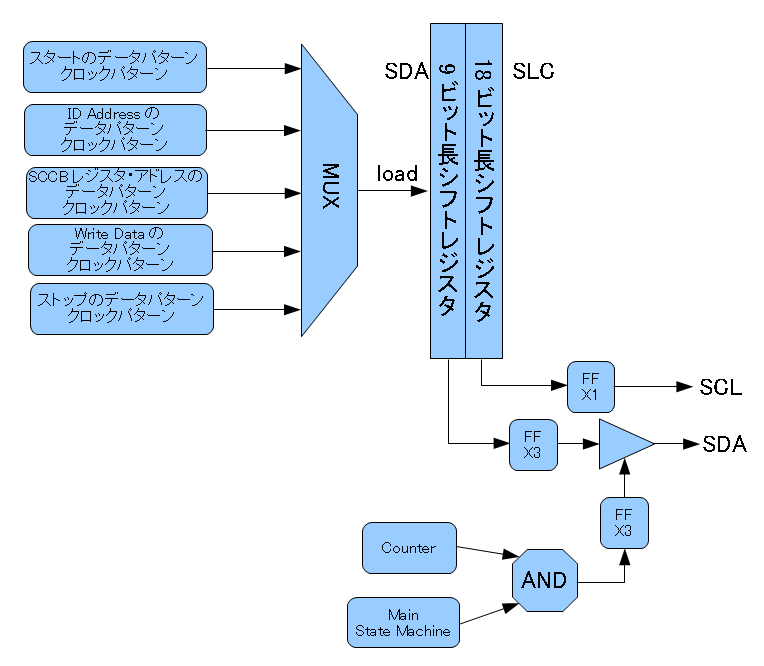

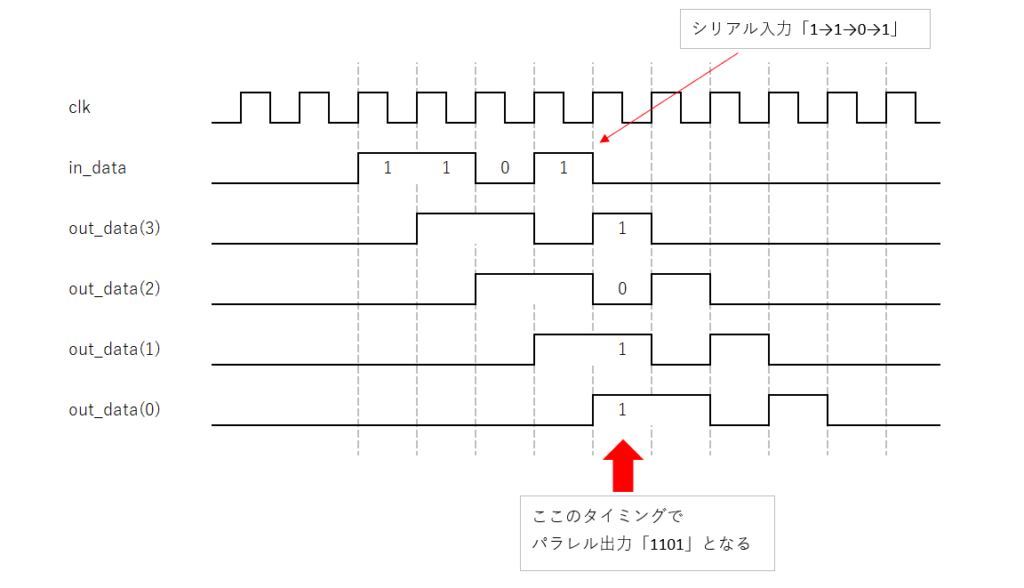

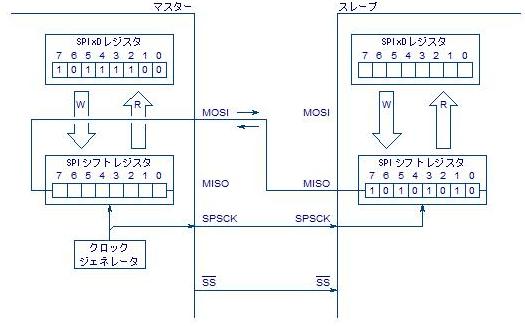

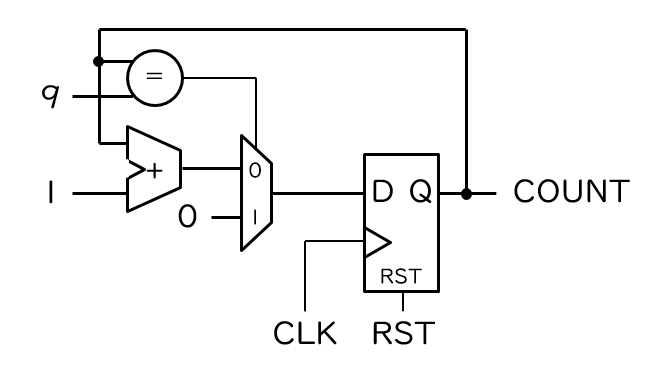

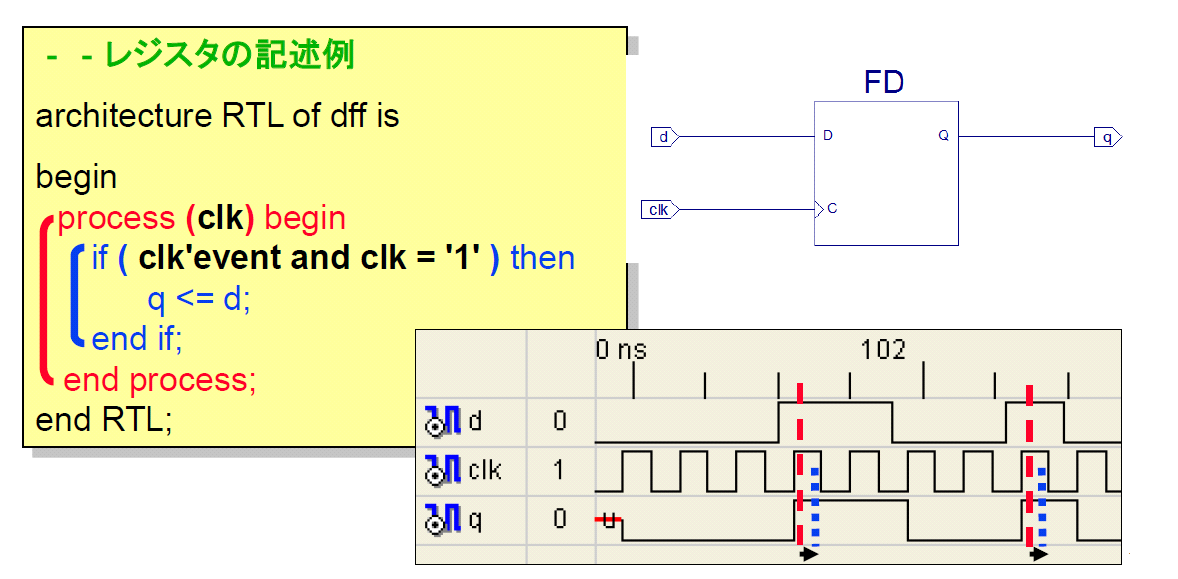

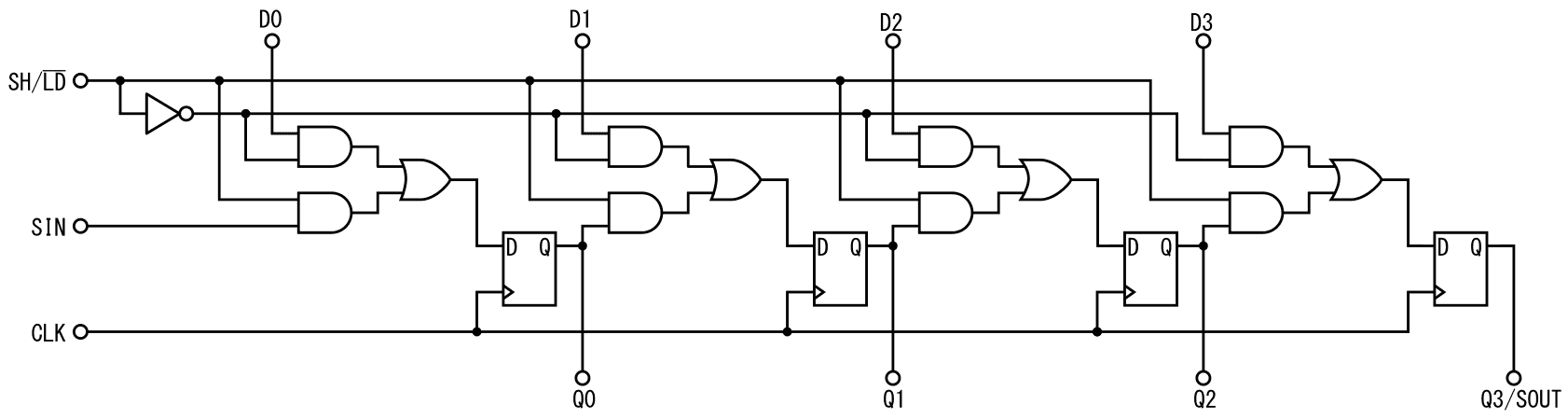

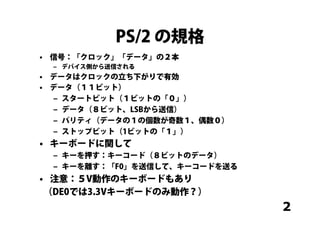

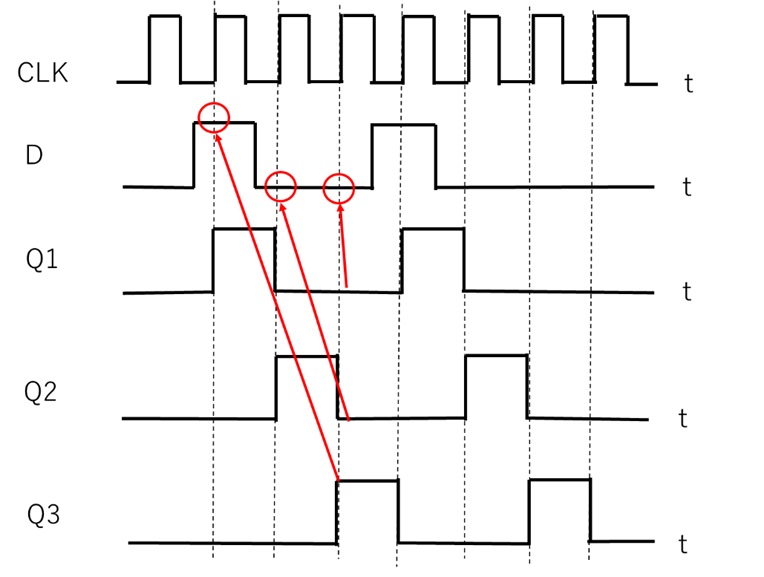

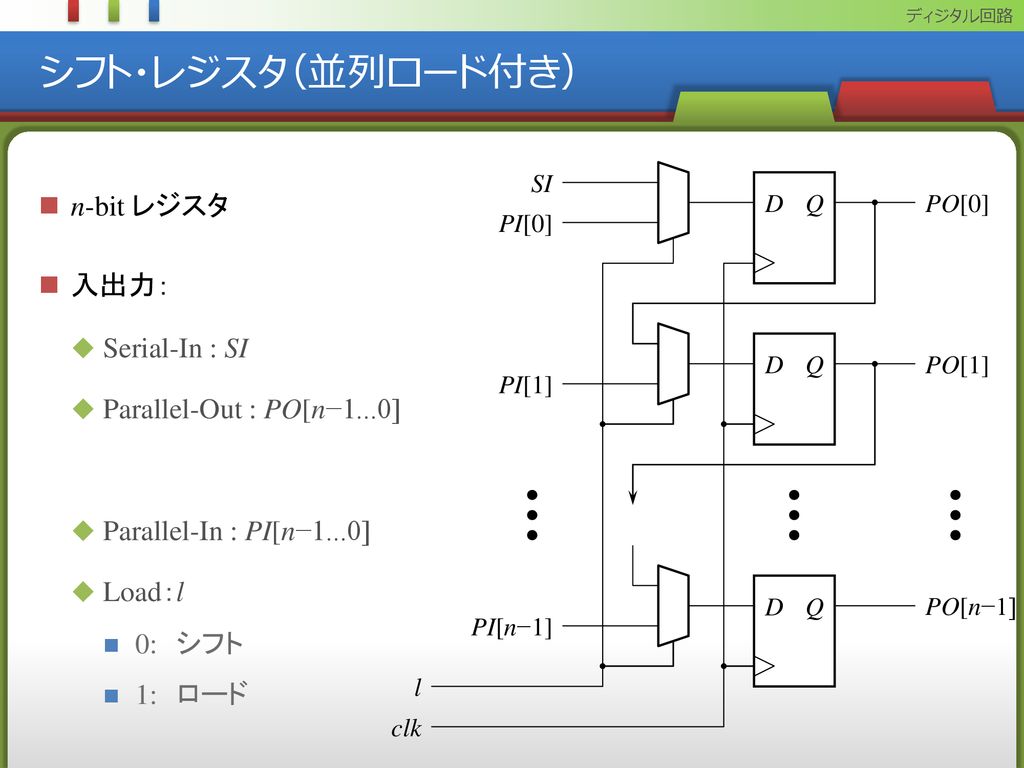

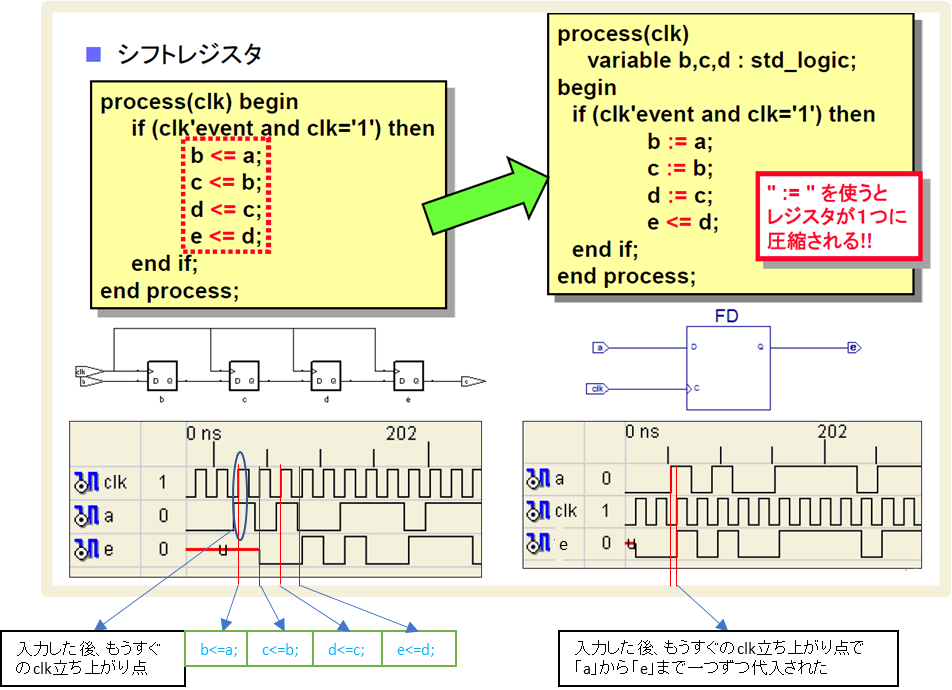

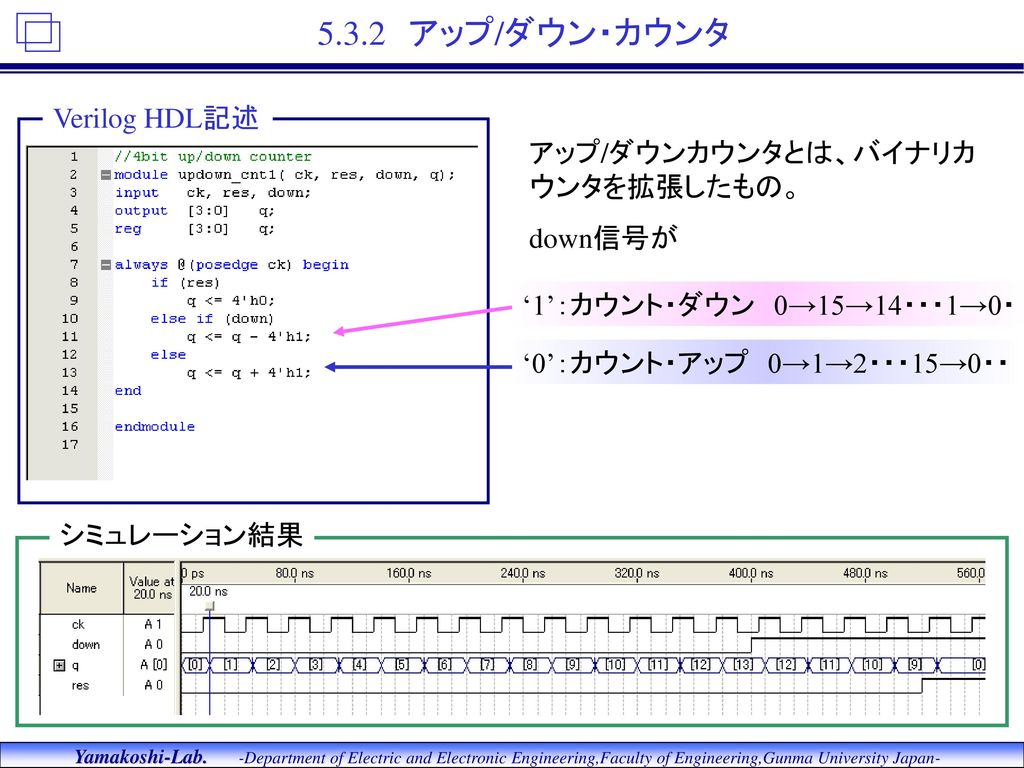

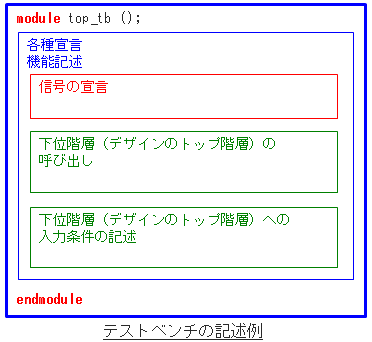

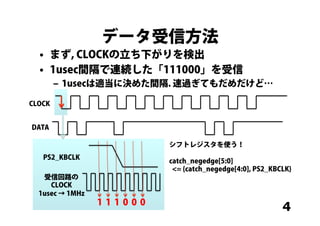

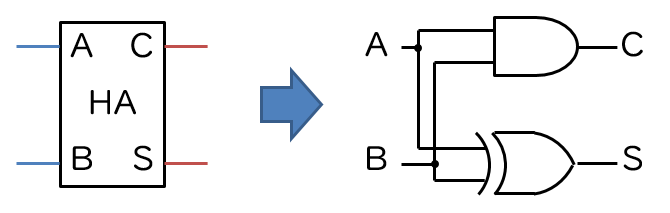

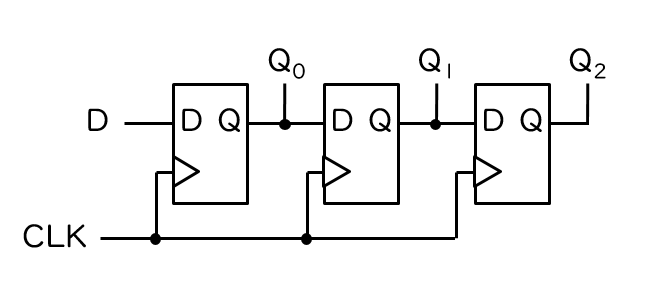

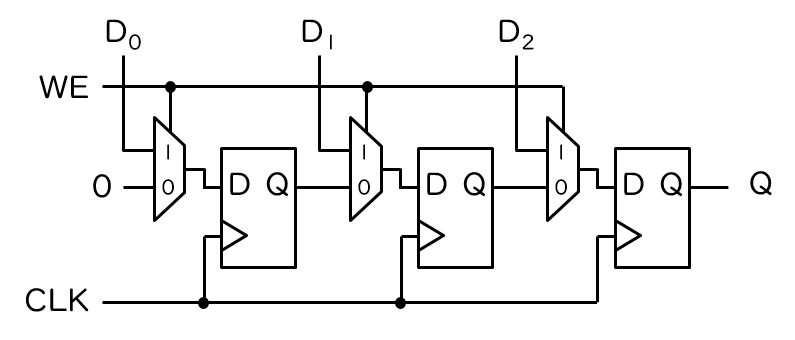

Verilog 多ビット シフトレジスタ- 次のVerilogシフトレジスタコードのヘルプを探しますか?次のコードが私に与えられました。私の仕事はそれを回路図形式に変換することです。 module shift_register( output reg シフトレジスタの回路図と記述法 (verilog, VHDL) まずシフトレジスタとは、FF (フリップフロップ)を複数用いて値を右から左へ、または左から右へシフトさせるものです。 よく使

Verilog 多ビット シフトレジスタのギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

| ||

|  | |

| ||

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

| ||

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

| ||

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

| ||

|  | |

|  | |

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  | |

| ||

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

| ||

| ||

「Verilog 多ビット シフトレジスタ」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  | |

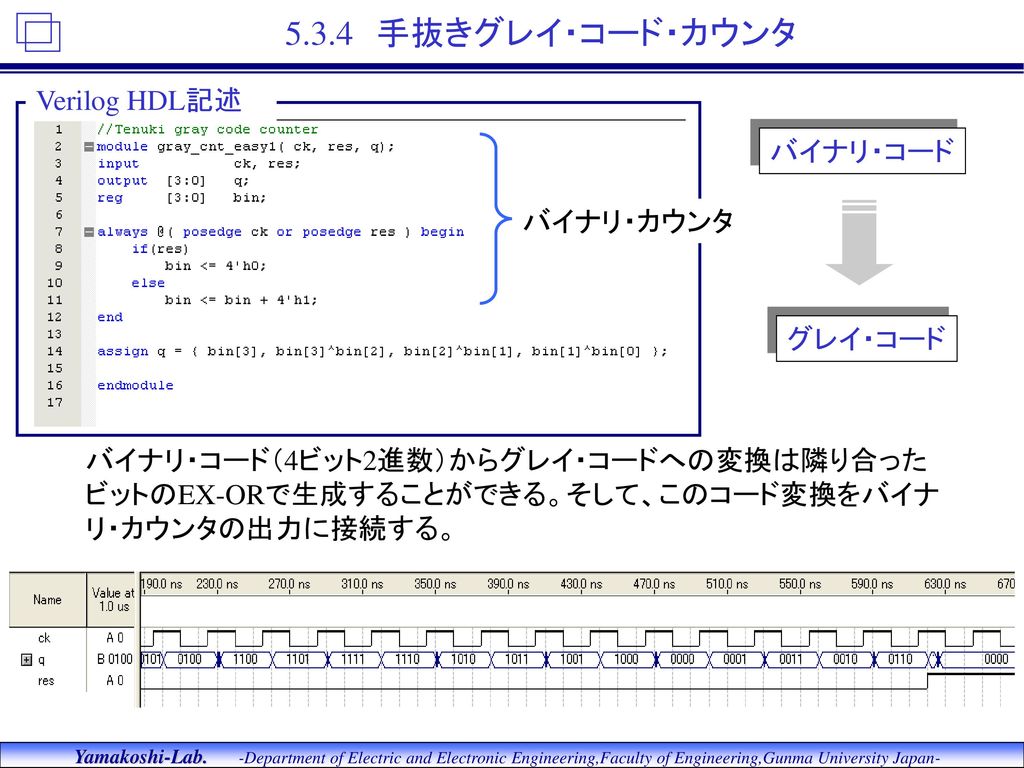

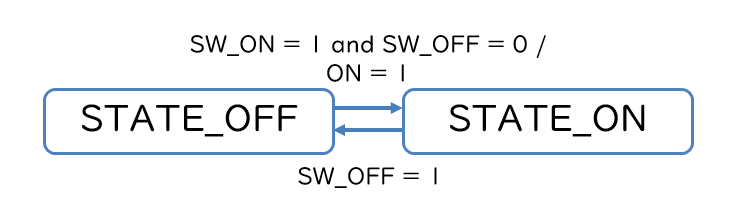

概要 遅延サイクルと幅を設定可能なシフトレジスタです。 意外とネットに記述が見当たらないので作成しました。 FF生成は本モジュールをパラメーターを変えて使いまわすと楽そうこれが代表的なシフトレジスタの記述法です。 ステートマシン 制御回路の設計でステートマシンは便利な記述です。 例えば下の状態遷移図を持つステートマシンの記述について考えてみます。 動作

Incoming Term: verilog シフトレジスタ, verilog シフトレジスタ 配列, verilog シフトレジスタ パラレルシリアル変換, verilog 多ビット シフトレジスタ, verilog generate シフトレジスタ,

コメント

コメントを投稿